## Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

#### **General Description**

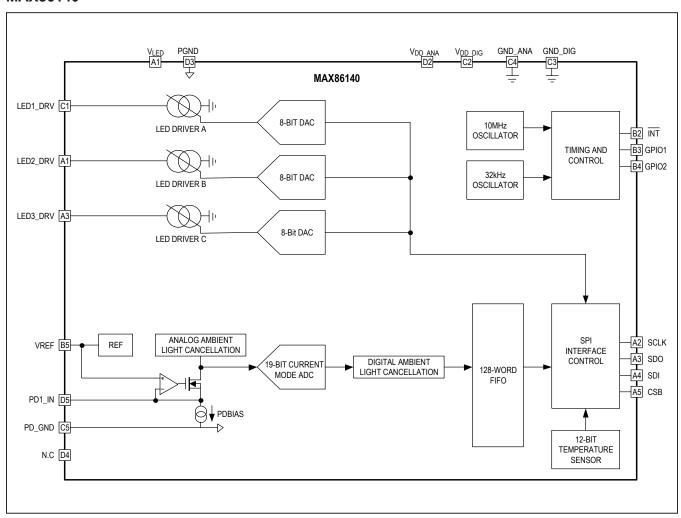

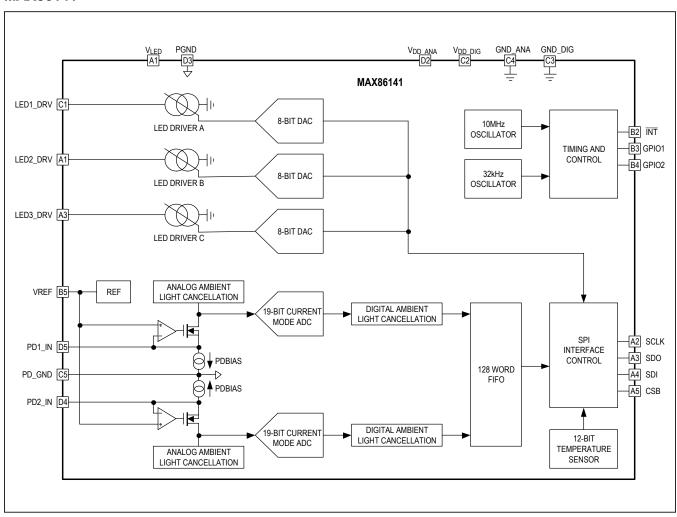

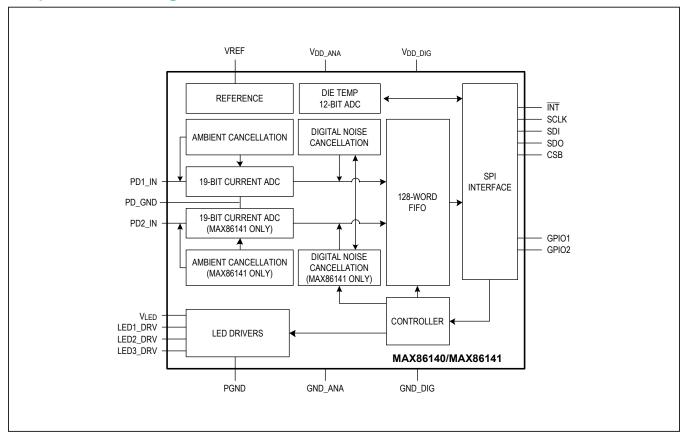

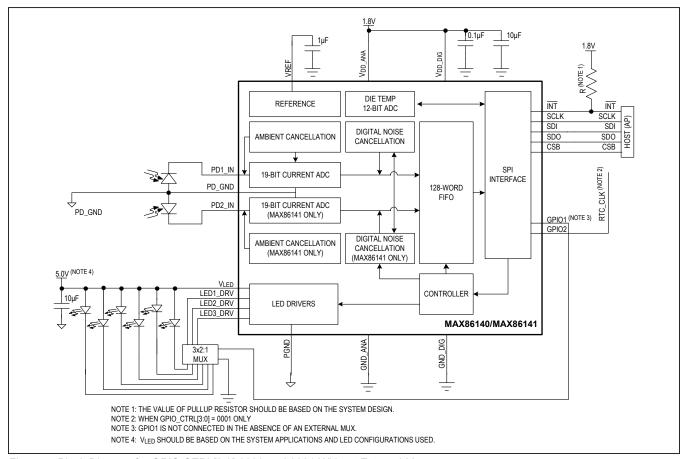

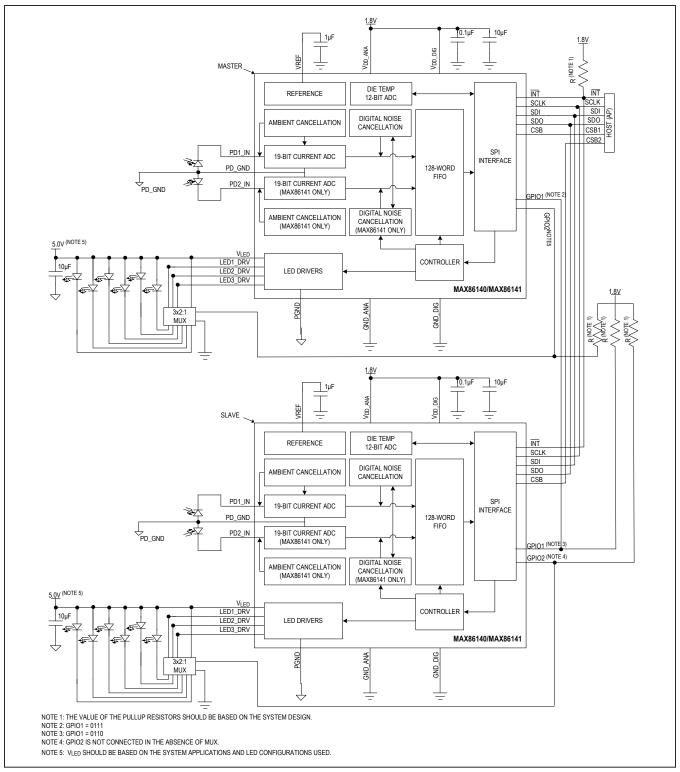

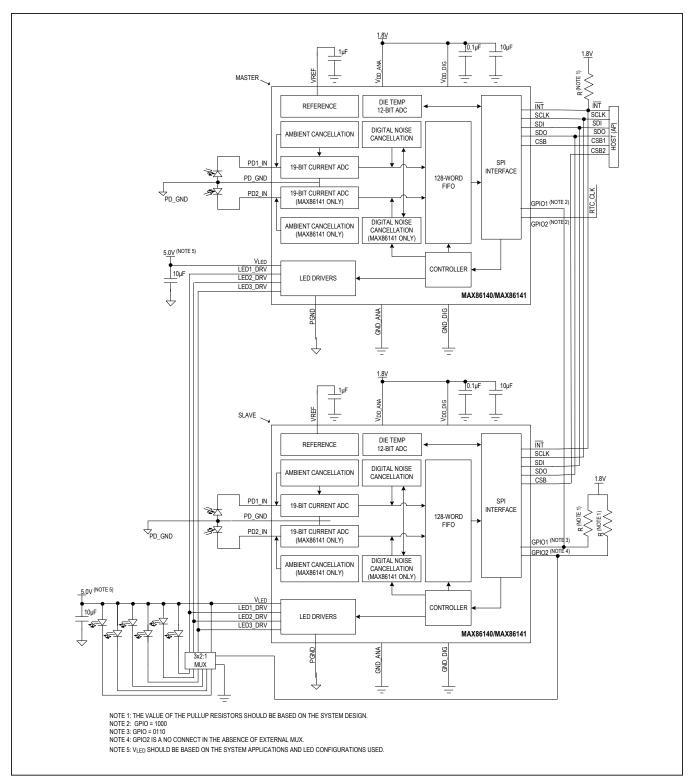

The MAX86140/MAX86141 are ultra-low-power, completely integrated, optical data acquisition systems. On the transmitter side, the MAX86140/MAX86141 have three programmable high-current LED drivers that can be configured to drive up to six LEDs using an external 3x2:1 mux. With two MAX86140/MAX86141 devices working in master-slave mode, the LED drivers can drive up to twelve LEDs using an external 3x2:1 mux. On the receiver side, MAX86140 consists of a single optical readout channel, while the MAX86141 has two optical readout channels that can operate simultaneously. The devices have lownoise signal conditioning analog front-end (AFE) including 19-bit ADC, an industry-lead ambient light cancellation (ALC) circuit, and a picket fence detect and replace function. Due to the low power consumption, compact size, ease of use, and industry-lead ambient light rejection capability of MAX86140/MAX86141, the devices are ideal for a wide variety of optical-sensing applications, such as pulse oximetry and heart rate detection.

The MAX86140/MAX86141 operate on a 1.8V main supply voltage and a 3.1V to 5.5V LED driver supply voltage. Both devices support a standard SPI compatible interface and fully autonomous operation. Each device has a large 128-word built-in FIFO. The MAX86140/MAX86141 is available in compact wafer-level package (WLP) (2.048 x 1.848mm) with 0.4mm ball pitch.

#### **Applications**

- Wearable Devices for Fitness, Wellness and Medical Applications

- Optimized for Wrist, Finger, Ear, and Other Locations

- Optimized Performance to Detect

- Optical Heart Rate

- Oxygen Saturation (SpO<sub>2</sub>)

- Muscle Oxygen Saturation (SmO<sub>2</sub> and StO<sub>2</sub>)

#### **Benefits and Features**

- Complete Single and Dual-Channel Optical Data Acquisition System

- Optimized Architecture for Transmissive and Reflective Heart Rate or SpO<sub>2</sub> Monitoring

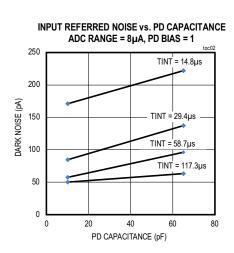

- Low Dark Current Noise of < 50pA RMS (Sample to Sample Variance)

- Lower Effective Dark Current Noise Achievable Through Multiple Sample Modes and On-Chip Averaging

- High-Resolution, 19-Bit Charge Integrating ADC

- Three Low-Noise, 8-Bit LED Current DACs

- Excellent Dynamic Range > 89dB in White Card Loop-Back Test (Sample-to-Sample Variance)

- Dynamic Range Extendable to > 104dB for SpO<sub>2</sub> and > 110dB for HRM with Multiple Sample Modes and On-Chip Averaging

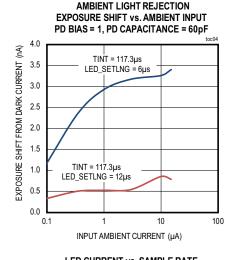

- Excellent Ambient Range and Rejection Capability

- > 100µA Ambient Photodetector Current

- > 70dB Ambient Rejection at 120Hz

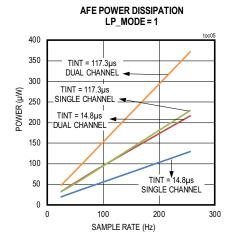

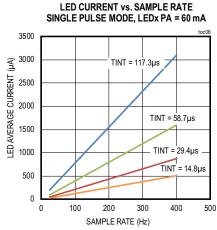

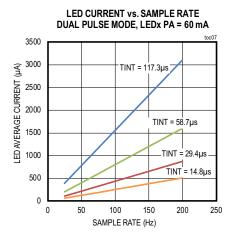

- Ultra-Low-Power Operation for Wearable Devices

- Low-Power Operation, Optical Readout Channel

10μA (typ) at 25sps

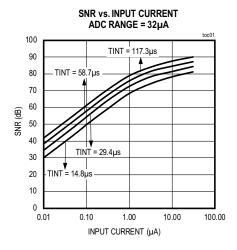

- Short Exposure Integration Period of 14.8μs, 29.4μs, 58.7μs, 117.3μs

- Low Shutdown Current = 0.6µA (typ)

- Rejection of Fast Ambient Transients

- Miniature 2.048 x 1.848mm, 5 x 4 0.4mm Ball Pitch WLP

- -40°C to +85°C Operating Temperature Range

Ordering Information appears at end of data sheet.

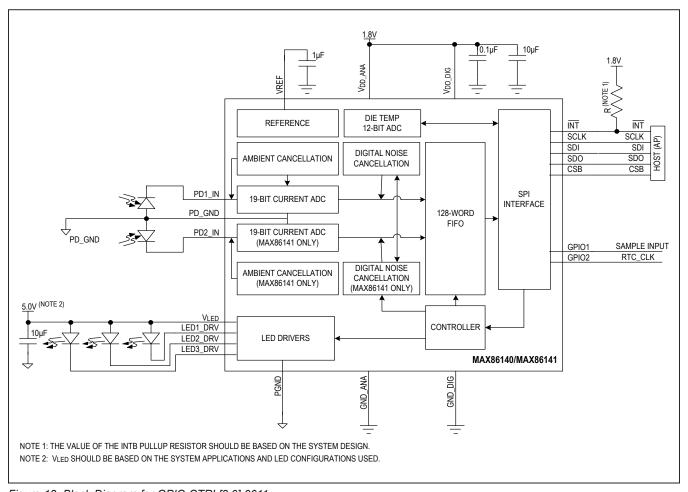

## **Detailed Block Diagrams**

#### **MAX86140**

## **Detailed Block Diagrams (continued)**

#### **MAX86141**

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

## **Absolute Maximum Ratings**

| V <sub>DD ANA</sub> to GND_ANA             | 0.3V to +2.2V                   | PD1_IN to GND_ANA                     | 0.3V to +2.2V  |

|--------------------------------------------|---------------------------------|---------------------------------------|----------------|

| V <sub>DD</sub> DIG to GND_ANA             | 0.3V to +2.2V                   | PD2_IN to GND_ANA                     | 0.3V to +2.2V  |

| V <sub>DD</sub> ANA to V <sub>DD</sub> DIG | 0.3V to +0.3V                   | PD_GND to GND_ANA                     | 0.3V to +0.3V  |

| PGND to GND_ANA                            | 0.3V to +0.3V                   | All other pins to GND_ANA             | 0.3V to +2.2V  |

| SCLK, SDO, SDI, CSB, INT, GPIO1,           |                                 | Output Short-Circuit Duration         | Continuous     |

| GPIO2 to GND_ANA                           | 0.3V to +6.0V                   | Continuous Input Current Into Any Pin |                |

| GND_DIG to GND_ANA                         | 0.3V to +0.3V                   | (except LEDx_DRV Pins)                | ±20mA          |

| V <sub>LED</sub> to PGND                   | 0.3V to +6.0V                   | Continuous Power Dissipation (WLP     |                |

| LED1_DRV to PGND                           | 0.3V to V <sub>LED</sub> + 0.3V | (derate 5.5mW/°C above +70°C))        | 440mW          |

| LED2_DRV to PGND                           | 0.3V to V <sub>LED</sub> + 0.3V | Operating Temperature Range           | 40°C to +85°C  |

| LED3_DRV to PGND                           | 0.3V to V <sub>LED</sub> + 0.3V | Storage Temperature Range             | 40°C to +105°C |

|                                            |                                 |                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 5 x 4 WLP

| PACKAGE CODE                           | N201A2+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | <u>21-100134</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 55.49°C/W                      |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

#### **Electrical Characteristics**

$(V_{DD\_ANA} = 1.8V, V_{DD\_DIG} = 1.8V, V_{LED} = 5.0V, PPGx\_ADC\_RGE = 16\mu A, PPG\_SR = 1024sps, PPG\_TINT = 14.8\mu s, LED\_SETLNG = 6\mu s, LEDx\_RGE = 31mA, C_{PD} = 65pF, PDBIASx = 0x1, I_{exposure} = 1\mu A, T_A = +25°C, min/max are from T_A = -40°C to +85°C, unless otherwise noted. (Note 1, 2))$

| PARAMETER                                   | SYMBOL           | CONDITI                                                                              | ONS               | MIN  | TYP   | MAX  | UNITS  |

|---------------------------------------------|------------------|--------------------------------------------------------------------------------------|-------------------|------|-------|------|--------|

| Readout Channel                             | ,                | •                                                                                    |                   |      |       | ,    |        |

| ADC Resolution                              |                  |                                                                                      |                   |      | 19    |      | bits   |

|                                             |                  | PPGx_ADC_RGE = 0x0                                                                   |                   |      | 4.0   |      |        |

| ADO 5 110 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                  | PPGx_ADC_RGE = 0x1                                                                   |                   |      | 8.0   |      |        |

| ADC Full Scale Input Current                |                  | PPGx_ADC_RGE = 0x2                                                                   |                   |      | 16.0  |      | μΑ     |

|                                             |                  | PPGx_ADC_RGE = 0x3                                                                   |                   |      | 32.0  |      |        |

|                                             |                  | PPG_TINT = 0x0                                                                       |                   |      | 14.8  |      |        |

| ADO lete enetice Time                       |                  | PPG_TINT = 0x1                                                                       |                   |      | 29.4  |      |        |

| ADC Integration Time                        | t <sub>INT</sub> | PPG_TINT = 0x2                                                                       |                   |      | 58.7  |      | μs     |

|                                             |                  | PPG_TINT = 0x3                                                                       |                   |      | 117.3 |      |        |

| Minimum PPG Sample Rate                     |                  | PPG_SR = 0x0A                                                                        |                   |      | 8     |      | sps    |

| Maximum PPG Sample Rate                     |                  | PPG_SR = 0x13                                                                        |                   |      | 4096  |      | sps    |

| Sample Rate Error                           |                  | From nominal as indicat table                                                        | ed in the PPG_SR  | -2   |       | +2   | %      |

| Maximum DC Ambient Light Rejection          | ALR              | ALC = on, ALC_OVF = 1                                                                |                   | 200  |       | μA   |        |

| AC Ambient Light Rejection                  | AC_ALRR          | ALC = on, I <sub>ambient</sub> = 1µ/<br>±0.4µA pk-pk 120Hz Sin                       |                   | 70   |       | dB   |        |

| DC Ambient Light Rejection                  |                  | ALC = on, I <sub>ambient</sub> modu<br>and 30µA, LED_SETLN<br>PPG_TINT = 117.3µs     |                   |      | 0.5   |      | nA     |

| Dark Current Offset                         | DC_O             | ALC = ON, PDBIASx = 0x                                                               | 0, ADD_OFFSET = 1 |      | ±1    | ,    | Counts |

|                                             |                  | PPG_TINT = 14.8µs                                                                    |                   |      | 262   | ,    |        |

| Dark Current Input Referred                 |                  | PPG_TINT = 29.4µs                                                                    |                   |      | 128   | ,    | pArms  |

| Noise                                       |                  | PPG_TINT = 58.7µs                                                                    |                   |      | 83    |      |        |

|                                             |                  | PPG_TINT = 117.3µs                                                                   |                   |      | 56    |      | pArms  |

|                                             |                  |                                                                                      | PDBIASx = 0x1     |      | 65    |      |        |

| Maximum Photodiode Input                    |                  | I <sub>ambient</sub> = 0μA, less                                                     | PDBIASx = 0x5     |      | 130   |      |        |

| Capacitance                                 | C <sub>pd</sub>  | than 1nA of code shift                                                               | PDBIASx = 0x6     |      | 260   |      | pF     |

|                                             |                  |                                                                                      | PDBIASx = 0x7     |      | 520   |      |        |

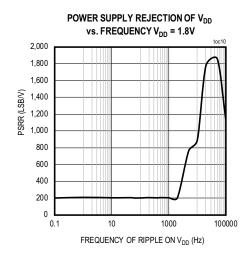

| VDD DC PSR                                  |                  | I <sub>ambient</sub> = 0μA, V <sub>DD_ANA</sub> = V <sub>DD_DIG</sub> = 1.7V to 2.0V |                   | -560 | -330  | +560 | LSB/V  |

| LED Driver                                  | -1               |                                                                                      |                   |      |       |      |        |

| LED Current Resolution                      |                  |                                                                                      |                   |      | 8     |      | Bits   |

| Driver DNL                                  |                  | LEDx_RGE = 124mA                                                                     |                   | -1   |       | 1    | LSB    |

| Driver INL                                  |                  | LEDx_RGE = 124mA                                                                     |                   |      | 0.6   |      | LSB    |

|                                             | _1               | LEDA_NOL = 124IIIA                                                                   |                   |      |       |      |        |

## **Electrical Characteristics (continued)**

$(V_{DD\_ANA} = 1.8V, V_{DD\_DIG} = 1.8V, V_{LED} = 5.0V, PPGx\_ADC\_RGE = 16\mu A, PPG\_SR = 1024sps, PPG\_TINT = 14.8\mu s, LED\_SETLNG = 6\mu s, LEDx\_RGE = 31mA, C_{PD} = 65pF, PDBIASx = 0x1, I_{exposure} = 1\mu A, T_A = +25°C, min/max are from T_A = -40°C to +85°C, unless otherwise noted. (Note 1, 2))$

| PARAMETER                        | SYMBOL                                       | CONDITIONS                                                                         |                |     | TYP  | MAX  | UNITS |  |

|----------------------------------|----------------------------------------------|------------------------------------------------------------------------------------|----------------|-----|------|------|-------|--|

|                                  |                                              |                                                                                    | LEDx_RGE = 0x0 |     | 31   |      |       |  |

| Full Scale LED Current           |                                              | LEDY DA - OVEE                                                                     | LEDx_RGE = 0x1 |     | 62   |      | A     |  |

| Full Scale LED Current           | I <sub>LED</sub>                             | LEDx_PA = 0xFF                                                                     | LEDx_RGE = 0x2 |     | 93   |      | mA    |  |

|                                  |                                              |                                                                                    | LEDx_RGE = 0x3 | 117 | 124  | 129  |       |  |

|                                  |                                              |                                                                                    | LEDx_RGE = 0x0 |     | 160  | 253  |       |  |

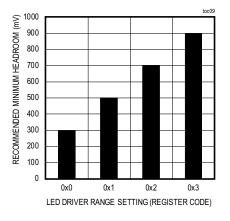

| Minimum output voltage           | V                                            | LEDx_PA = 0xFF,<br>95% of the desired LED                                          | LEDx_RGE = 0x1 |     | 317  |      | mV    |  |

| Minimum output voltage           | V <sub>OL</sub>                              | current                                                                            | LEDx_RGE = 0x2 |     | 495  |      | IIIV  |  |

|                                  |                                              |                                                                                    | LEDx_RGE = 0x3 |     | 700  |      |       |  |

| LED Driver DC PSR                |                                              | VLEDx_DRV = 0.9V, LED<br>V <sub>LED</sub> = 3.1V to 5.5V, LED                      |                |     | -1   | +400 | µA/V  |  |

| LED DIIVEI DC PSK                |                                              | V <sub>DD_ANA</sub> = V <sub>DD_DIG</sub> = 1<br>T <sub>A</sub> = +25°C, LEDx_PA = |                | 110 | 1410 | μΑνν |       |  |

| LED1 Driver Compliance Interrupt | LED1 <sub>COMP</sub>                         |                                                                                    |                |     | 180  |      | mV    |  |

| Internal Die Temperature Senso   | or                                           |                                                                                    |                |     |      |      |       |  |

| Temperature Sensor Accuracy      |                                              | T <sub>A</sub> = +25°C                                                             |                |     | 1    |      | °C    |  |

| Temperature Sensor Minimum Range |                                              | Temperature error < 5°C                                                            |                |     | -40  |      | °C    |  |

| Temperature Sensor Maximum Range |                                              | Temperature error < 5°C                                                            |                |     | 85   |      | °C    |  |

| Temperature ADC Acquisition Time |                                              |                                                                                    |                |     | 29   |      | ms    |  |

| Power Supply                     |                                              |                                                                                    |                |     |      |      |       |  |

| Power Supply Voltage             | V <sub>DD_ANA</sub> ,<br>V <sub>DD_DIG</sub> | Verified during PSRR Test                                                          |                | 1.7 | 1.8  | 2.0  | V     |  |

| LED Supply Voltage               | V <sub>LED</sub>                             | Verified during PSRR Tes                                                           | st             | 3.1 |      | 5.5  | V     |  |

## **Electrical Characteristics (continued)**

$(V_{DD\_ANA} = 1.8V, V_{DD\_DIG} = 1.8V, V_{LED} = 5.0V, PPGx\_ADC\_RGE = 16\mu A, PPG\_SR = 1024sps, PPG\_TINT = 14.8\mu s, LED\_SETLNG = 6\mu s, LEDx\_RGE = 31mA, C_{PD} = 65pF, PDBIASx = 0x1, I_{exposure} = 1\mu A, T_A = +25°C, min/max are from T_A = -40°C to +85°C, unless otherwise noted. (Note 1, 2))$

| PARAMETER                | SYMBOL           | CONDITI                                                                                                 | ONS             | MIN | TYP   | MAX  | UNITS |

|--------------------------|------------------|---------------------------------------------------------------------------------------------------------|-----------------|-----|-------|------|-------|

|                          |                  | MAX86140, Single LED E<br>PPG_SR = 4096sps, LP_<br>LEDxPA = 0mA                                         |                 |     | 660   | 780  |       |

|                          |                  | MAX86140, Single LED                                                                                    | PPG_SR = 256sps |     | 80    |      | μA    |

|                          |                  | Exposure/Sample,                                                                                        | PPG_SR = 100sps |     | 32    |      |       |

|                          |                  | PW = 14.8µs, LP_MODE                                                                                    | PPG_SR = 50sps  |     | 16    |      |       |

|                          |                  | = 0x1, LEDx_PA = 0mA                                                                                    | PPG_SR = 25sps  |     | 8.5   |      |       |

|                          |                  | MAX86140, Double LED                                                                                    | Single pulse    |     | 42    |      | μA    |

|                          |                  | Exposure/Sample, PPG_SR = 84sps, PW = 14.8µs, LP_MODE = 0x1, LEDx_PA = 0mA                              | Double pulse    |     | 89    |      | μΑ    |

| VDD Supply Current       | I <sub>DD</sub>  | MAX86141, Single LED<br>PPG_SR = 4096sps, LP<br>LEDxPA = 0mA                                            |                 |     | 978   | 1170 |       |

|                          |                  | MAX86141, Single LED Exposure/Sample, LP_BOOST = 1,                                                     | PPG_SR = 256sps |     | 115.5 |      | μA    |

|                          |                  |                                                                                                         | PPG_SR = 100sps |     | 46    |      | j '   |

|                          |                  |                                                                                                         | PPG_SR = 50sps  |     | 23    |      |       |

|                          |                  | LEDx_PA = 0mA                                                                                           | PPG_SR = 25sps  |     | 11    |      |       |

|                          |                  | MAX86141, Two LED                                                                                       | Single pulse    |     | 60    |      | μΑ    |

|                          |                  | Exposure/Sample, PPG_SR<br>= 84sps, LP_BOOST = 1,<br>LEDx_PA = 0mA                                      | Double pulse    |     | 130   |      | μA    |

|                          |                  | Die Temperature mode, schannel(s) disabled                                                              |                 | 8   |       | μΑ   |       |

|                          |                  | Single LED exposure per Sample, PPG_<br>TINT = 117.3µs, Single-Pulse,<br>PPG_SR = 256sps, LEDx_PA = 0mA |                 |     | 0.22  |      |       |

|                          |                  | Single LED exposure                                                                                     | PPG_SR = 256sps |     | 1880  |      | μA    |

|                          |                  | per Sample, PPG_TINT                                                                                    | PPG_SR = 100sps |     | 735   |      |       |

| VLED Supply Current      | I <sub>LED</sub> | = 117.3µs, Single-Pulse,                                                                                | PPG_SR = 50sps  |     | 370   |      |       |

|                          |                  | LEDx_PA = 62mA                                                                                          | PPG_SR=25sps    |     | 185   |      |       |

|                          |                  | Two LED exposure per                                                                                    | Single-Pulse    |     | 1240  |      |       |

|                          |                  | sample, PPG_TINT =<br>117.3µs, LEDx_PA =<br>62mA, PPG_SR = 84sps                                        | Dual-Pulse      |     | 2480  |      | μА    |

| VDD Current in Shutdown  |                  | T <sub>A</sub> = +25°C                                                                                  |                 |     | 0.6   | 2.5  | μA    |

| VLED Current in Shutdown |                  | T <sub>A</sub> = +25°C                                                                                  |                 |     |       | 1    | μA    |

#### **Electrical Characteristics (continued)**

$(V_{DD\_ANA} = 1.8V, V_{DD\_DIG} = 1.8V, V_{LED} = 5.0V, PPGx\_ADC\_RGE = 16\mu A, PPG\_SR = 1024sps, PPG\_TINT = 14.8\mu s, LED\_SETLNG = 6\mu s, LEDx\_RGE = 31mA, C_{PD} = 65pF, PDBIASx = 0x1, I_{exposure} = 1\mu A, T_A = +25°C, min/max are from T_A = -40°C to +85°C, unless otherwise noted. (Note 1, 2))$

| PARAMETER                           | SYMBOL                         | CONDITIONS                                                                  | MIN                  | TYP  | MAX   | UNITS |

|-------------------------------------|--------------------------------|-----------------------------------------------------------------------------|----------------------|------|-------|-------|

| Digital I/O Characteristics         |                                |                                                                             |                      |      |       |       |

| SDO Output Low Voltage              | V <sub>OL_SDO</sub>            | I <sub>SINK</sub> = 2mA                                                     |                      |      | 0.4   | V     |

| SDO Output High Voltage             | V <sub>OH</sub> <sub>SDO</sub> | I <sub>SOURCE</sub> = 2mA                                                   | V <sub>DD</sub> -0.4 |      |       | V     |

| Open-Drain Output Low Voltage       | V <sub>OL_OD</sub>             | I <sub>SINK</sub> = 6mA, INTB, GPIO1, GPIO2                                 |                      |      | 0.4   | V     |

| Input Voltage Low                   | V <sub>IL</sub>                | SDI, SCLK, CSB, GPIO1, GPIO2                                                |                      |      | 0.4   | V     |

| Input Voltage High                  | V <sub>IH</sub>                | SDI, SCLK, CSB, GPIO1, GPIO2                                                | 1.4                  |      |       | V     |

| In most I book and a sign           | \/                             | SDI, SCLK, CSB                                                              |                      | 330  |       | \/    |

| Input Hysteresis                    | $V_{HYS}$                      | GPIO1, GPO2                                                                 |                      | 240  |       | mV    |

| Input Leakage Current               | I <sub>IN</sub>                | V <sub>IN</sub> = 0V, T <sub>A</sub> = +25°C (SDI, SCLK, CSB, GPIO1, GPIO2) |                      | 0.01 | 1     | μΑ    |

| Input Capacitance                   | C <sub>IN</sub>                | SDI, SCLK, CSB, GPIO1, GPIO2                                                |                      | 10   |       | pF    |

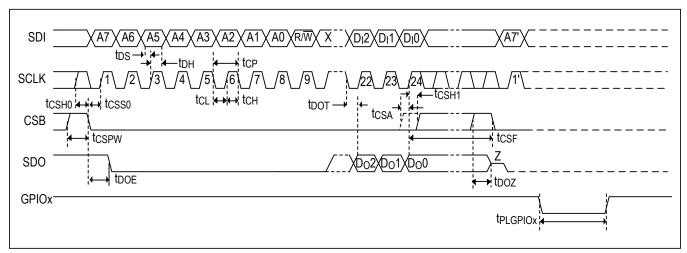

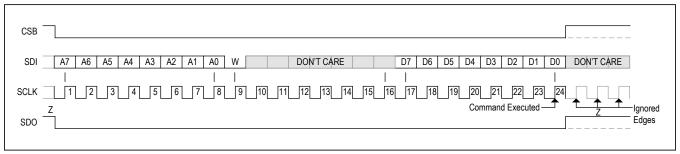

| SPI Timing Charateristics (Note     | 3)                             |                                                                             |                      |      |       |       |

| SCLK Frequency                      | f <sub>SCLK</sub>              |                                                                             |                      |      | 8     | MHz   |

| SCLK Period                         | t <sub>CP</sub>                |                                                                             | 125                  |      |       | ns    |

| SCLK Pulse Width High               | t <sub>CH</sub>                |                                                                             | 40                   |      |       | ns    |

| SCLK Pulse Width Low                | t <sub>CL</sub>                |                                                                             | 40                   |      |       | ns    |

| CSB Fall to SCLK Rise Setup Time    | t <sub>CSS0</sub>              | To 1st SCLK rising edge                                                     | 20                   |      |       | ns    |

| CSB Fall to SCLK Rise Hold Time     | t <sub>CSH0</sub>              | Applies to inactive rising edge preceding 1st rising edge                   | 5                    |      |       | ns    |

| CSB Rise to SCLK Rise Hold Time     | t <sub>CSH1</sub>              | Applies to 24th rising edge                                                 | 500                  |      |       | ns    |

| SCLK Rise to CSB Fall               | t <sub>CSF</sub>               | Applies to 24th rising edge                                                 | 500                  |      |       | ns    |

| CSB Pulse Width High                | tcspw                          |                                                                             | 250                  |      |       | ns    |

| SDI to SCLK Rise Setup Time         | t <sub>DS</sub>                |                                                                             | 10                   |      |       | ns    |

| SDI to SCLK Rise Hold Time          | t <sub>DH</sub>                |                                                                             | 10                   |      |       | ns    |

| SCLK Fall to SDO Transition         | t <sub>DOT</sub>               | C <sub>LOAD</sub> = 50pF                                                    |                      |      | 35    | ns    |

| CSB Fall to SDO Enabled             | t <sub>DOE</sub>               | C <sub>LOAD</sub> = 0pF                                                     | 12                   |      |       | ns    |

| CSB Rise to SDO Hi-Z                | t <sub>DOZ</sub>               | Disable Time                                                                |                      |      | 25    | ns    |

| GPIO1 External Sync Pulse Width     | t <sub>PLGPIO1</sub>           |                                                                             | 5                    |      |       | μs    |

| GPIO2 External Clock Input (Note 4) | f <sub>GPIO2</sub>             | External Sample Reference Clock on GPIO2                                    | 31900                |      | 32868 | Hz    |

| GPIO2 External Clock Pulse<br>Width | tpwgpi02                       |                                                                             | 1                    |      |       | μs    |

- **Note 1:** All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by Maxim Integrated's bench or proprietary automated test equipment (ATE) characterization.

- Note 2: All other register settings assumed to be POR status unless otherwise noted.

- Note 3: Guaranteed by design. Not production tested.

- **Note 4:** See Register Map/PPG Configuration 2 (0x12) section for the sample rate by the external clock frequency. The sample rate shifts if the external clock frequency drifts.

## **Typical Operating Characteristics**

$(V_{DD\_ANA} = V_{DD\_DIG} = 1.8V, V_{LED} = 5.0V, GND\_ANA = GND\_DIG = PGND = 0V, T_A = +25$ °C, unless otherwise noted.)

# AMBIENT REJECTION vs. FREQUENCY RESPONSE 10 10 10 10 10 100 1000 10000 10000 10000 10000 10000 10000

## **Typical Operating Characteristics (continued)**

$(V_{DD\_ANA} = V_{DD\_DIG} = 1.8V, V_{LED} = 5.0V, GND\_ANA = GND\_DIG = PGND = 0V, T_A = +25$ °C, unless otherwise noted.)

#### SUGGESTED LED DRIVER HEADROOM VOLTAGE

# AVERAGE V<sub>DD</sub> SHUTDOWN CURRENT V<sub>DD</sub> = 1.8 V 12 10 (Y) 8 4 2 0 -50 0 50 100 TEMPERATURE (°C)

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

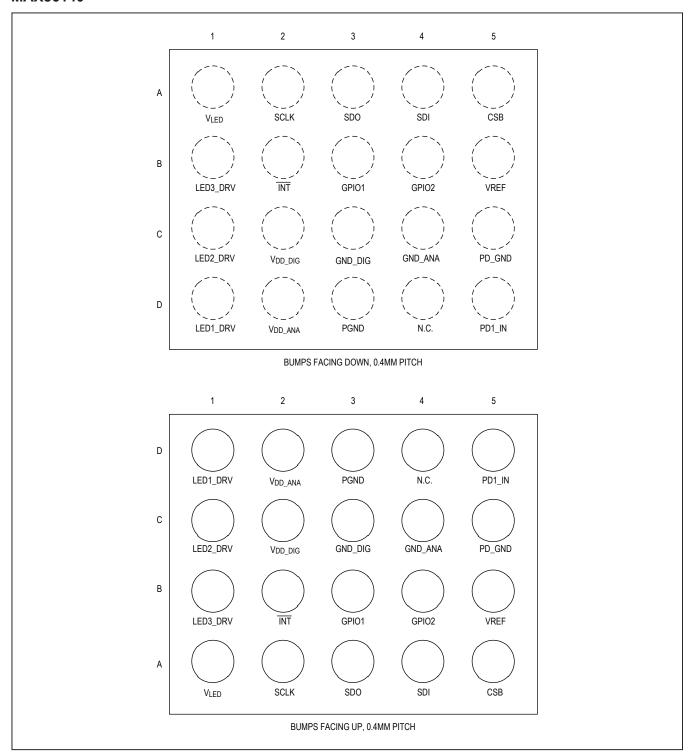

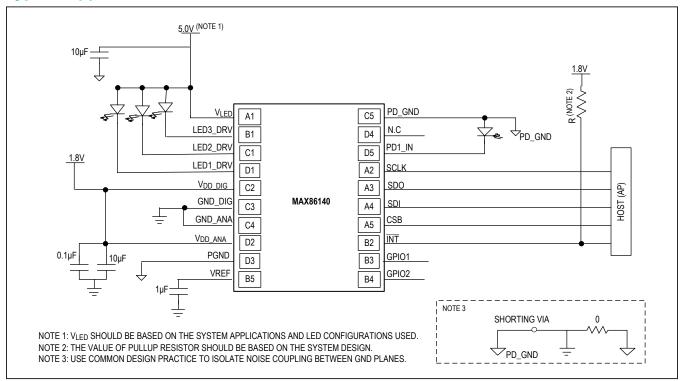

## **Pin Configurations**

#### **MAX86140**

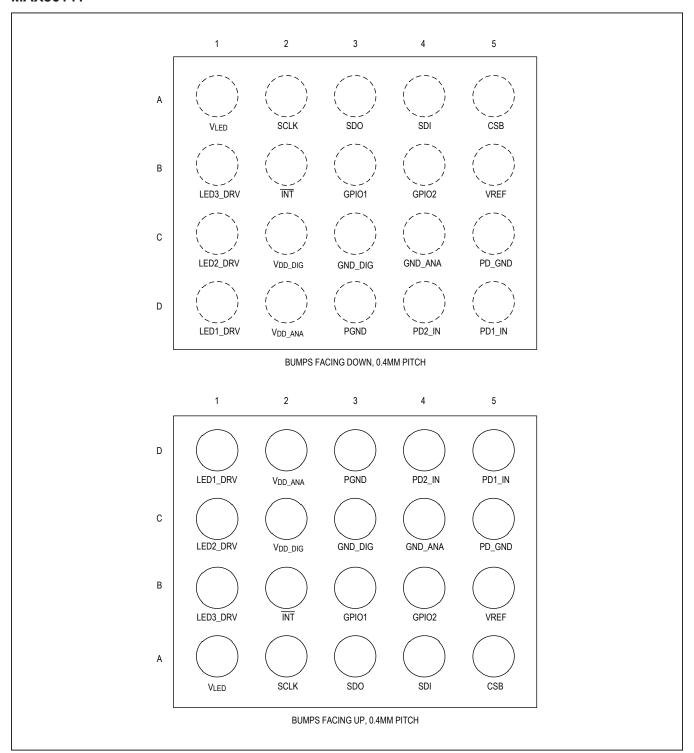

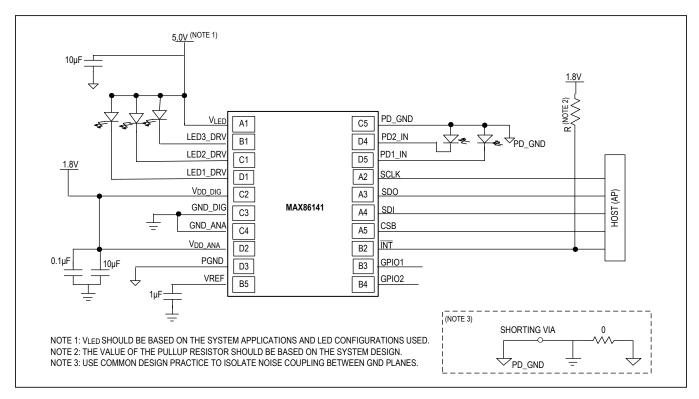

## **Pin Configurations (continued)**

#### **MAX86141**

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

## **Pin Description**

| PIN          |          |                     | EUNCTION                                                                                                                                           |  |  |  |  |  |

|--------------|----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MAX86140     | MAX86141 | NAME FUNCTION       |                                                                                                                                                    |  |  |  |  |  |

| Power        | ļ.       |                     |                                                                                                                                                    |  |  |  |  |  |

| C2           | C2       | V <sub>DD_DIG</sub> | Digital Logic Supply. Connect to externally-regulated supply. Bypass to GND_DIG                                                                    |  |  |  |  |  |

| C3           | C3       | GND_DIG             | Digital Logic and Digital Pad Return. Connect to PCB Ground.                                                                                       |  |  |  |  |  |

| D2           | D2       | V <sub>DD_ANA</sub> | Analog Supply. Connect to externally-regulated supply. Bypass with a 0.1µF capacitor as close as possible to bump and a 10µF capacitor to GND_ANA. |  |  |  |  |  |

| C4           | C4       | GND_ANA             | Analog Power Return. Connect to PCB Ground.                                                                                                        |  |  |  |  |  |

| A1           | A1       | V <sub>LED</sub>    | LED Power Supply Input. Connect to external voltage supply. Bypass with a 10μF capacitor to PGND.                                                  |  |  |  |  |  |

| D3           | D3       | PGND                | LED Power Return. Connect to PCB Ground.                                                                                                           |  |  |  |  |  |

| Control Inte | rface    |                     |                                                                                                                                                    |  |  |  |  |  |

| A2           | A2       | SCLK                | SPI Clock                                                                                                                                          |  |  |  |  |  |

| A3           | A3       | SDO                 | SPI Data Ouput                                                                                                                                     |  |  |  |  |  |

| A4           | A4       | SDI                 | SPI Data Input                                                                                                                                     |  |  |  |  |  |

| A5           | A5       | CSB                 | SPI Chip select                                                                                                                                    |  |  |  |  |  |

| B2           | B2       | ĪNT                 | Interrupt. Programmable open-drain Interrupt output signal pin (active-low).                                                                       |  |  |  |  |  |

| В3           | В3       | GPIO1               | General Purpose I/O. Open-drain when programmed as output (active-low).                                                                            |  |  |  |  |  |

| B4           | B4       | GPIO2               | General Purpose I/O. Open-drain when programmed as output (active-low).                                                                            |  |  |  |  |  |

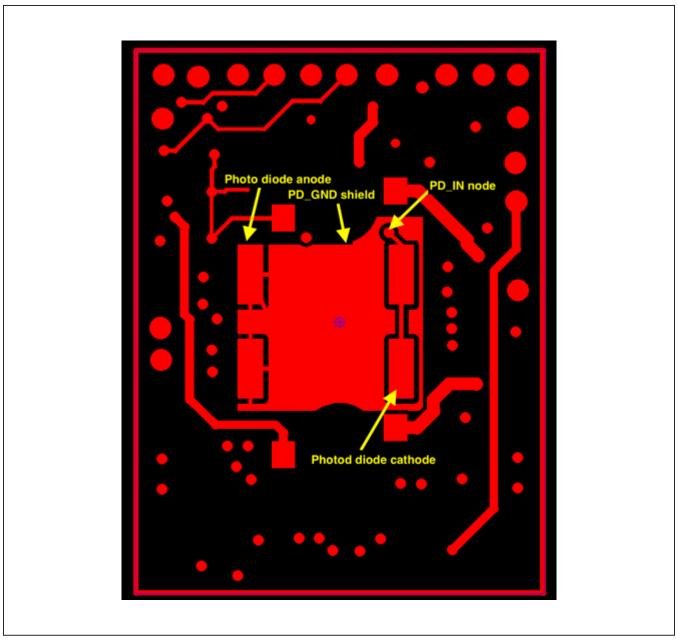

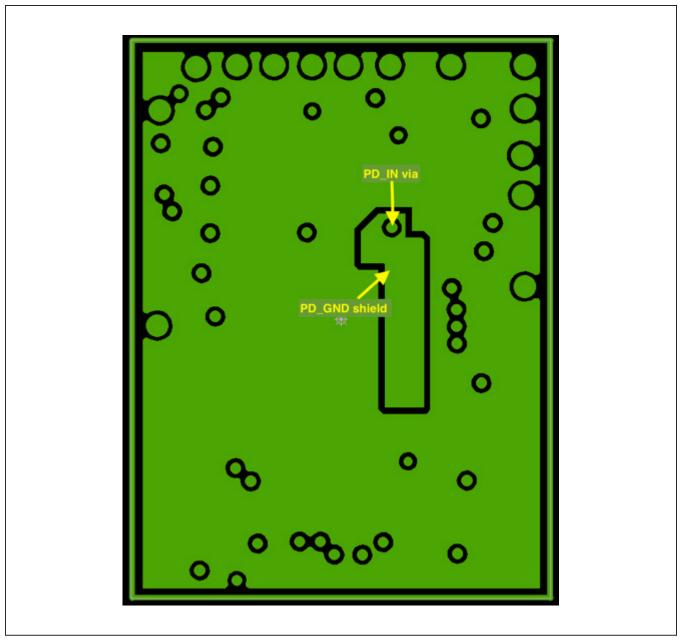

| Optical Pins | 3        |                     |                                                                                                                                                    |  |  |  |  |  |

| _            | D4       | PD2_IN              | Photodiode Cathode Input                                                                                                                           |  |  |  |  |  |

| D5           | D5       | PD1_IN              | Photodiode Cathode Input                                                                                                                           |  |  |  |  |  |

| C5           | C5       | PD_GND              | Photodiode Anode                                                                                                                                   |  |  |  |  |  |

| D1           | D1       | LED1_DRV            | LED Output Driver 1. Connect the LED cathode to LED1_DRV and its anode to the $V_{LED}$ supply                                                     |  |  |  |  |  |

| C1           | C1       | LED2_DRV            | LED Output Driver 2. Connect the LED cathode to LED2_DRV and its anode to the $V_{\text{LED}}$ supply                                              |  |  |  |  |  |

| B1           | B1       | LED3_DRV            | LED Output Driver 3 Connect the LED cathode to LED3_DRV and its anode to the V <sub>LED</sub> supply.                                              |  |  |  |  |  |

| Reference    |          |                     |                                                                                                                                                    |  |  |  |  |  |

| B5           | B5       | VREF                | Internal Reference Decoupling Point. Bypass with a 1µF capacitor to GND_ANA.                                                                       |  |  |  |  |  |

| N.C.         |          |                     |                                                                                                                                                    |  |  |  |  |  |

| D4           |          | N.C.                | No Connection. Connect to unconnected PCB pad for mechanical stability. N.C. pins should not be connected to any signal, power, or ground pins.    |  |  |  |  |  |

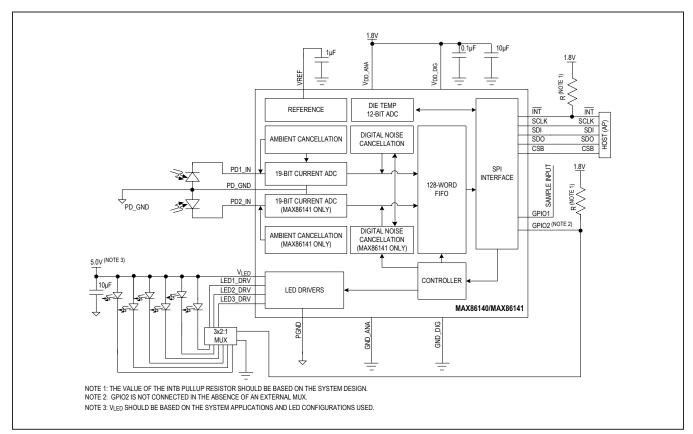

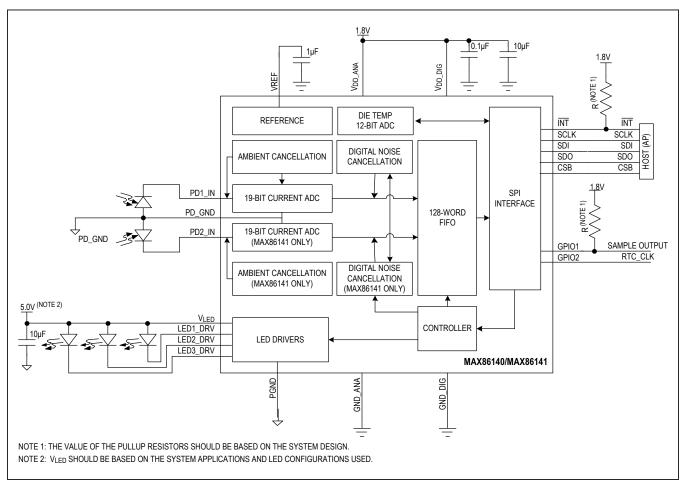

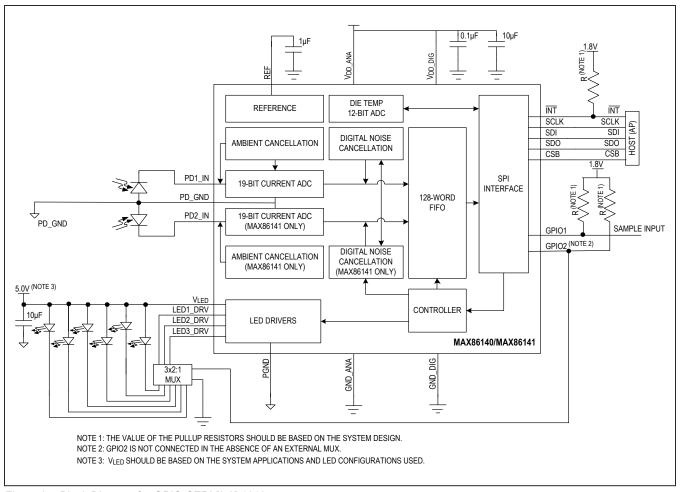

## **Simplified Block Diagram**

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

#### **Detailed Description**

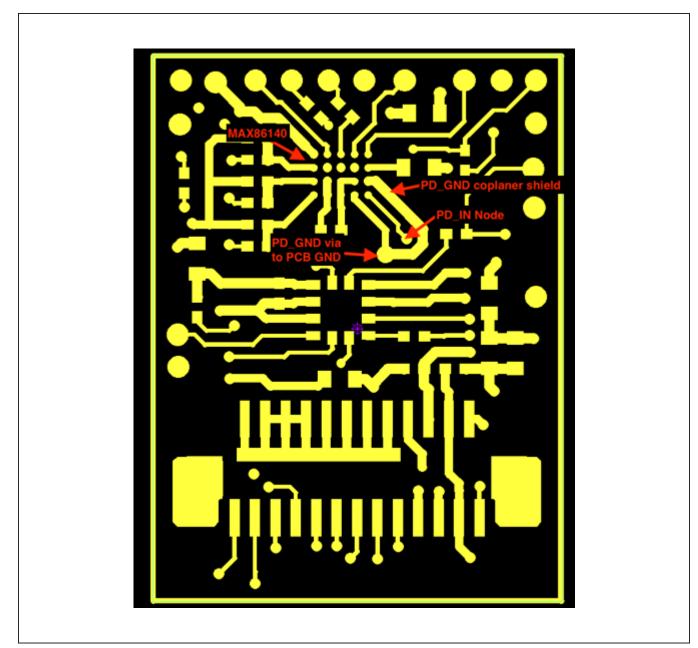

The MAX86140/MAX86141 are complete integrated optical data acquisition systems, ideal for optical pulse oximetry and heart rate detection applications. Both parts have been designed for the demanding requirements of mobile and wearable devices and require minimal external hardware components are necessary for integration into a wearable device. They include high-resolution, optical readout signal processing channels with robust ambient light cancellation and high-current LED driver DACs to form a complete optical readout signal chain.

The MAX86140/MAX86141 are fully adjustable through software registers and the digital output data is stored in a 128-word FIFO within the IC. The FIFO allows the MAX86140/MAX86141 to be connected to a microcontroller or processor on a shared bus, where the data is not being read continuously from the MAX86140/MAX86141's registers. Both operate in fully autonomous modes for low power battery applications.

The MAX86140 consists of a single optical readout channel, while the MAX86141 incorporates dual optical readout channels that operate simultaneously. Both parts have three LED drivers and are well suited for a wide variety of optical sensing applications.

The MAX86140/MAX86141 operate on a 1.8V main supply voltage, with a separate 3.1V to 5.5V LED driver power supply. Both devices have flexible timing and shutdown configurations as well as control of individual blocks so an optimized measurement can be made at minimum power levels.

#### **Optical Subsystem**

The optical subsystem in the MAX86140/MAX86141 is composed of ambient light cancellation (ALC), a continuous-time sigma-delta ADC, and proprietary discrete time filter. ALC incorporates a proprietary scheme to cancel ambient light generated photodiode current, allowing the sensor to work in high ambient light conditions. The optical ADC has programmable full-scale ranges of  $4\mu A$  to  $32\mu A$ . The internal ADC is a continuous time oversampling sigma delta converter with 19-bit resolution.

The ADC output data rate can be programmed from 8sps (samples per second) to 4096sps per channel. The MAX86140/MAX86141 includes a proprietary discrete time filter to reject 50Hz/60Hz interference and changing residual ambient light from the sensor measurements.

The MAX86140/MAX86141 supports Dynamic Power Down mode (Low-Power mode) in which the power consumption is decreased between samples. This mode is only supported for sample rates 128sps and below. For more details on the power consumption at each sample rates, refer to the *Electrical Characteristics* table.

#### **LED Driver**

The MAX86140/MAX86141 integrates three precision LED driver-current DACs that modulate LED pulses for a variety of optical measurements. The LED current DACs have 8-bits of dynamic range with four programmable full-scale ranges of 31mA, 62mA, 94mA, and 124mA. The LED drivers are low dropout current sources, allowing for low-noise, power-supply independent LED currents to be sourced at the lowest supply voltage possible; therefore minimizing LED power consumption. The LED pulse width can be programmed from 14.8µs to 117.3µs to allow the algorithms to optimize SpO<sub>2</sub> and HR accuracy at the lowest dynamic power consumption dictated by the application.

#### **FIFO Configuration**

The FIFO is 128 sample depth and is designed to support various data types, as shown in <u>Table 2</u>. Each sample width is 3 bytes, which includes a 5-bit tag width. The tag embedded in the FIFO\_DATA is used to identify the source of each sample data. The description of each Tag is as shown in Table 3.

#### LED Sequence Control (address 0x20 ~ 0x22)

The data format in the FIFO, as well as the sequencing of exposures, are controlled by the LED Sequence Registers through LEDC1 through LEDC6. There are six LED Sequence Data Items available, as shown in <a href="Table 1">Table 1</a>. The exposure sequence cycles through the LED Sequence bit fields, starting from LEDC1 to LEDC6. The first LED Sequence field set to NONE (0000) ends the sequence.

**Table 1. LED Sequence Control Registers**

| ADDRESS | REG-<br>ISTER<br>NAME         | DE-<br>FAULT<br>VALUE | В7         | В6         | B5 | B4 | В3   | B2     | B1      | В0 |

|---------|-------------------------------|-----------------------|------------|------------|----|----|------|--------|---------|----|

| 0x20    | LED<br>Sequence<br>Register 1 | 00                    | LEDC2[3:0] |            |    |    |      | LEDC   | 1[3:0]  |    |

| 0x21    | LED<br>Sequence<br>Register 2 | 00                    | LEDC4[3:0] |            |    |    | LEDC | 3[3:0] |         |    |

| 0x22    | LED<br>Sequence<br>Register 3 | 00                    |            | LEDC6[3:0] |    |    |      | LEDC   | C5[3:0] |    |

<u>Table 2</u> lists the codes for exposures selected in the LED sequence control registers.

**Table 2. LED Sequence Register Data Type**

| LEDCN[3:0] | DATA TYPE                                  |  |  |  |  |

|------------|--------------------------------------------|--|--|--|--|

| 0000       | NONE                                       |  |  |  |  |

| 0001       | LED1                                       |  |  |  |  |

| 0010       | LED2                                       |  |  |  |  |

| 0011       | LED3                                       |  |  |  |  |

| 0100       | LED1 and LED2 pulsed simultaneously        |  |  |  |  |

| 0101       | LED1 and LED3 pulsed simultaneously        |  |  |  |  |

| 0110       | LED2 and LED3 pulsed simultaneously        |  |  |  |  |

| 0111       | LED1, LED2, and LED3 pulsed simultaneously |  |  |  |  |

| 1000       | Pilot on LED1                              |  |  |  |  |

| 1001       | DIRECT AMBIENT                             |  |  |  |  |

| 1010       | LED4 (external mux control)                |  |  |  |  |

| 1011       | LED5 (external mux control)                |  |  |  |  |

| 1100       | LED6 (external mux control)                |  |  |  |  |

| 1101       | Reserved                                   |  |  |  |  |

| 1110       | Reserved                                   |  |  |  |  |

| 1111       | Reserved                                   |  |  |  |  |

## Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

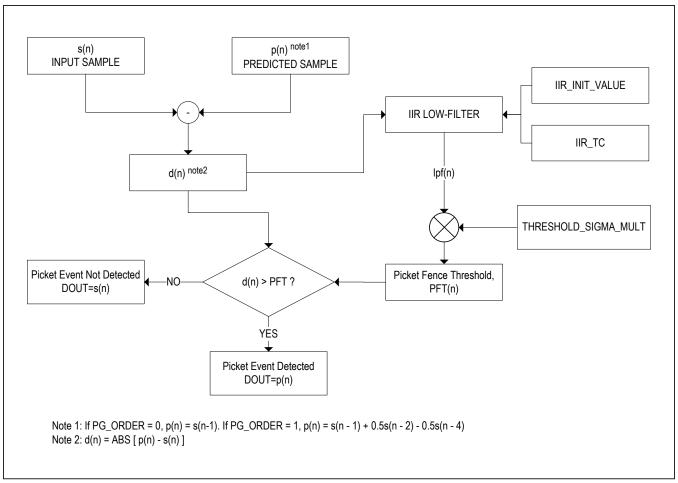

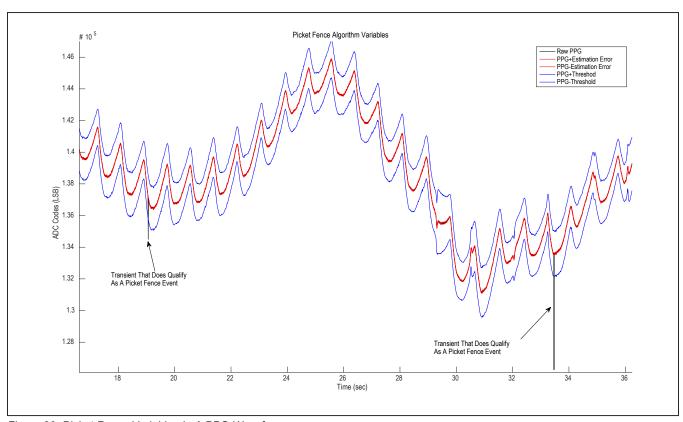

<u>Table 3</u> shows the format of the FIFO data along with the associated Tag. In a sample if a picket fence event is detected, the predicted value is pushed to the FIFO along with its tag (PPFx\_LEDCx\_DATA).

**Table 3. FIFO Data and Tag**

| TAG[4:0] | DATA TYPE       | COMMENTS                                                           |

|----------|-----------------|--------------------------------------------------------------------|

| 00001    | PPG1 LEDC1 DATA | If LEDC1 is non-zero                                               |

| 00010    | PPG1 LEDC2 DATA | If LEDC1 and LEDC2 are non-zero                                    |

| 00011    | PPG1 LEDC3 DATA | If LEDC1, LEDC2 and LEDC3 are non-zero                             |

| 00100    | PPG1 LEDC4 DATA | If LEDC1, LEDC2, LEDC3, and LEDC4 are non-zero                     |

| 00101    | PPG1 LEDC5 DATA | If LEDC1, LEDC2, LEDC3, LEDC4, and LEDC5 are non-zero              |

| 00110    | PPG1 LEDC6 DATA | If LEDC1, LEDC2, LEDC3, LEDC4, LEDC5, and LEDC6 are non-zero       |

| 00111    | PPG2 LEDC1 DATA | If LEDC1 is non-zero                                               |

| 01000    | PPG2 LEDC2 DATA | If LEDC1 and LEDC2 are non-zero                                    |

| 01001    | PPG2 LEDC3 DATA | If LEDC1, LEDC2, and LEDC3 are non-zero                            |

| 01010    | PPG2 LEDC4 DATA | If LEDC1, LEDC2, LEDC3, and LEDC4 are non-zero                     |

| 01011    | PPG2 LEDC5 DATA | If LEDC1, LEDC2, LEDC3, LEDC4, and LEDC5 are non-zero              |

| 01100    | PPG2 LEDC6 DATA | If LEDC1, LEDC2, LEDC3, LEDC4, LEDC5, and LEDC6 are non-zero       |

| 01101    | PPF1 LEDC1 DATA | If LEDC1 is non-zero (Picket Fence Event)                          |

| 01110    | PPF1 LEDC2 DATA | If LEDC1 and LEDC2 are non-zero (Picket Fence Event)               |

| 01111    | PPF1 LEDC3 DATA | If LEDC1, LEDC2, and LEDC3 are non-zero (Picket Fence Event)       |

| 10000    | Reserved        |                                                                    |

| 10001    | Reserved        |                                                                    |

| 10010    | Reserved        |                                                                    |

| 10011    | PPF2 LEDC1 DATA | If LEDC1 is non-zero (Picket Fence Event)                          |

| 10100    | PPF2 LEDC2 DATA | If LEDC1 and LEDC2 are non-zero (Picket Fence Event)               |

| 10101    | PPF2 LEDC3 DATA | If LEDC1, LEDC2, and LEDC3 are non-zero (Picket Fence Event)       |

| 10110    | Reserved        |                                                                    |

| 10111    | Reserved        |                                                                    |

| 11000    | Reserved        |                                                                    |

| 11001    | PROX1 DATA      | Only PILOT LED1 for LEDC1 is used                                  |

| 11010    | PROX2 DATA      | Only PILOT LED1 for LEDC1 is used                                  |

| 11011    | Reserved        |                                                                    |

| 11100    | Reserved        |                                                                    |

| 11101    | Reserved        |                                                                    |

| 11110    | INVALID DATA    | This tag indicates that there was an attempt to read an empty FIFO |

| 11111    | TIME STAMP      | If TIME_STAMP_EN = 1, this is TIME_STAMP                           |

There are seven registers that control how the FIFO is configured and read out. These registers are illustrated below.

**Table 4. PPG Configuration**

| AD-<br>DRESS | REGISTER<br>NAME        | В7                 | В6                   | B5                | B4             | В3                | B2              | B1         | В0 |  |

|--------------|-------------------------|--------------------|----------------------|-------------------|----------------|-------------------|-----------------|------------|----|--|

| 0x04         | FIFO Write Pointer      |                    |                      | _                 |                | FIFO_WR_PTR[6:0]  |                 |            |    |  |

| 0x05         | FIFO Read Pointer       |                    |                      | -                 |                | FIFO_RD_PTR[6:0]  |                 |            |    |  |

| 0x06         | Overflow Counter        |                    |                      | -                 |                |                   | OVF_COU         | INTER[6:0] |    |  |

| 0x07         | FIFO Data<br>Counter    |                    | FIFO_DATA_COUNT[7:0] |                   |                |                   |                 |            |    |  |

| 0x08         | FIFO Data<br>Register   |                    |                      |                   | FIFC           | D_DATA[7:0]       |                 |            |    |  |

| 0x09         | FIFO<br>Configuration 1 | - FIFO_A_FULL[6:0] |                      |                   |                |                   |                 |            |    |  |

| 0x0A         | FIFO<br>Configuration 2 | _                  | _                    | TIME_<br>STAMP_EN | FLUSH_<br>FIFO | FIFO_<br>STAT_CLR | A_FULL_<br>TYPE | FIFO_RO    | _  |  |

#### Write Pointer (Register 0x04)

FIFO\_WR\_PTR[6:0] points to the FIFO location where the next item will be written. This pointer advances for each item pushed on to the FIFO by the internal conversion process. The write pointer is a 7-bit counter and will wrap around to count 0x00 on the next item after count 0x7F.

#### Read Pointer (Register 0x05)

FIFO\_RD\_PTR[6:0] points to the location from where the next item from the FIFO will be read via the serial interface. This advances each time an item is read from the FIFO. The read pointer can be both read and written to. This allows an item to be reread from the FIFO if it has not already been overwritten. The read pointer is updated from a 7-bit counter and will wrap around to count 0x00 from count 0x7F.

#### Overflow Counter (Register 0x06)

OVF\_COUNTER[6:0] logs the number of items lost if the FIFO is not read in a timely fashion. This counter holds/ saturates at count value 0x7F. When a complete item is popped from the FIFO (when the read pointer advances), the OVF\_COUNTER is reset to zero. This counter is essentially a debug tool. It should be read immediately before reading the FIFO in order to check if an overflow condition has occurred.

#### FIFO Data Counter (Register 0x07)

FIFO\_DATA\_COUNT[7:0] is a read-only register which holds the number of items available in the FIFO for the host to read. This increments when a new item is pushed to the FIFO, and decrements when the host reads an item from the FIFO.

#### FIFO Data (Register 0x08)

FIFO\_DATA[7:0] is a read-only register used to retrieve data from the FIFO. It is important to burst read the item from the FIFO. Each item is three bytes. So burst reading three bytes at FIFO\_DATA register via the serial interface advances the FIFO\_RD\_PTR. The format and data type of the data stored in the FIFO is determined by the Tag associated with data. Readout from the FIFO follows a progression defined by LED Sequence Control registers as well. This configuration is best illustrated by a few examples.

Assume it is desired to perform a  $SpO_2$  measurement and also monitor the ambient level on the photodiode to adjust the IR and red LED intensity. To perform this measurement, configure the following registers:

| LED Sequence Control |                           |

|----------------------|---------------------------|

| LEDC1 = 0x1          | (LED1 exposure)           |

| LEDC2 = 0x2          | (LED2 exposure)           |

| LEDC3 = 0x9          | (DIRECT AMBIENT exposure) |

| LEDC4 = 0x0          | (NONE)                    |

| LEDC5 = 0x0          | (NONE)                    |

| LEDC6 = 0x0          | (NONE)                    |

| PPG Configuration    |                           |

| PPG1_ADC_RGE[1:0]    | (PPG1 Gain Range Control) |

| PPG2_ADC_RGE[1:0]    | (PPG2 Gain Range Control) |

| PPG_TINT[1:0]        | (LED Pulse-Width Control) |

| PPG_SR[3:0]          | (Sample Rate)             |

| LED Pulse Amplitude  |                           |

| LED1_PA[7:0]         | (LED1 Drive Current)      |

| LED2_PA[7:0]         | (LED2 Drive Current)      |

When done so the sample sequence and the data format in the FIFO follows the following time/location sequence.

```

tag 1, PPG1 LED1 data

tag 7, PPG2 LED1 data

tag 2, PPG1 LED2 data

tag 8, PPG2 LED2 data

tag 3, PPG1 Ambient data

tag 9, PPG2 Ambient data

tag 1, PPG1 LED1 data

tag 7, PPG2 LED1 data

tag 2, PPG1 LED2 data

tag 8, PPG2 LED2 data

tag 3, PPG1 Ambient data

tag 9, PPG2 Ambient data

tag 1, PPG1 LED1 data

tag 7, PPG2 LED1 data

tag 2, PPG1 LED2 data

tag 8, PPG2 LED2 data

tag 3, PPG1 Ambient data

tag 9, PPG2 Ambient data

where:

```

PPGm LED1 data = the ambient corrected exposure data from LED1 in PPGm channel PPGm LED2 data = the ambient corrected exposure data from LED2 in PPGm channel PPGm Ambient data = the direct ambient sample in PPGm channel m = 1 of PPG1 channel, and 2 for PPG2 channel

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

For a second example, assume it is desired to pulse LED1 and LED2 simultaneously while also monitoring the ambient level.

| LED Sequence Control |                           |  |  |  |

|----------------------|---------------------------|--|--|--|

| LEDC1 = 0x4          | (LED1 and LED2 exposure)  |  |  |  |

| LEDC2 = 0x9          | (DIRECT AMBIENT exposure) |  |  |  |

| LEDC3 = 0x0          | (NONE)                    |  |  |  |

| LEDC4 = 0x0          | (NONE)                    |  |  |  |

| LEDC5 = 0x0          | (NONE)                    |  |  |  |

| LEDC6 = 0x0          | (NONE)                    |  |  |  |

In this case, the sequencing in the FIFO will then be:

```

tag 1, PPG1 LED1+LED2 data

```

tag 7, PPG2 LED1+LED2 data

tag 2, PPG 1 Ambient data

tag 8, PPG 2 Ambient data

tag 1, PPG1 LED1+LED2 data

tag 7, PPG2 LED1+LED2 data

tag 2, PPG1 Ambient data

tag 8, PPG2 Ambient data

.

tag 1, PPG1 LED1+LED2 data

tag 7, PPG2 LED1+LED2 data

tag 2, PPG1 Ambient data

tag 8, PPG2 Ambient data

where:

PPGm LED1+LED2 data = the ambient corrected exposure data from LED1 and LED2 for PPGm channel PPGm Ambient data = the direct ambient corrected sample for PPGm channel

The number of bytes of data for the PPG channel is given by: 2 x 3 x K x N

#### where:

K = the number of active exposures as defined in the LED Sequence Control registers 0x20, 0x21, and 0x22.

N = the number of samples in the FIFO

To calculate the number of available items one can perform the following pseudo-code:

```

read the OVF_COUNTER register

read the FIFO_DATA_COUNT register

if OVF_COUNTER == 0 //no overflow occurred

NUM_AVAILABLE_SAMPLES = FIFO_DATA_COUNT

else

NUM_AVAILABLE_SAMPLES = 128 // overflow occurred and data has been lost

endif

```

$\underline{\text{Table 6}}$  shows the FIFO data format depends on the data type being stored. Optical data, whether full ambient corrected LED exposure, ambient corrected proximity or direct ambient sampled data is left-justified, as shown in  $\underline{\text{Table 6}}$ . Bits F23:F19 of the FIFO word contains the tag that identifies the data.

**Table 6. Optical FIFO Data Format**

| FIFO DATA FORMAT (FIFO_DATA[23:14])         |     |     |     |     |     |     |     |     |     |

|---------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Tag (TAG[4:0]) ADC Value (FIFO_DATA[18:14]) |     |     |     |     |     |     |     |     |     |

| F23                                         | F22 | F21 | F20 | F19 | F18 | F17 | F16 | F15 | F14 |

| T4                                          | Т3  | T2  | T1  | T0  | O18 | 017 | O16 | O15 | 014 |

| FIFO DATA FORMAT (FIFO_DATA[13:4]) |     |  |  |  |  |  |    |  |

|------------------------------------|-----|--|--|--|--|--|----|--|

| ADC Value (FIFO_DATA[13:4])        |     |  |  |  |  |  |    |  |

| F13 F12 F11 F10 F9 F8 F7 F6 F5 F4  |     |  |  |  |  |  | F4 |  |

| O13                                | O13 |  |  |  |  |  |    |  |

| FIFO DATA FORMAT (FIFO_DATA[3:0]) |    |    |    |  |  |

|-----------------------------------|----|----|----|--|--|

| ADC Value (FIFO_DATA[3:0])        |    |    |    |  |  |

| F3                                | F2 | F1 | F0 |  |  |

| O3                                | O2 | O1 | 00 |  |  |

#### FIFO\_A\_FULL (address 0x09)

The FIFO\_A\_FULL[6:0] field in the FIFO Configuration 1 register (0x09) sets the watermark for the FIFO and determines when the A\_FULL bit in the Interrupt\_Status register (0x00) gets asserted. The A\_FULL bit will be set when the FIFO contains 128 minus FIFO\_A\_FULL[6:0] items. When the FIFO is almost full, if the A\_FULL\_EN mask bit in the Interrupt\_Enable register (0x03) is set, then A\_FULL bit gets asserted in the Interrupt Status 1 register and this bit is routed to the INT pin on the serial interface. This condition should prompt the applications processor to read samples off of the FIFO before it fills. The A\_FULL bit is cleared when the status register is read.

The application processor can read both the FIFO\_WR\_PTR and FIFO\_RD\_PTR to calculate the number of items available in the FIFO, or just read the OVF\_COUNTER and FIFO\_DATA\_COUNT registers, and read as many items as it needs to empty the FIFO. Alternatively, if the applications always responds much faster than the selected sample rate, it could just read 128 minus FIFO\_A\_FULL[6:0] items when it gets A\_FULL interrupt and be assured that all data from the FIFO is read.

#### FIFO\_RO (Address 0x0A)

The FIFO\_RO bit in the FIFO Configuration 2 register (0x0A) determines whether samples get pushed on to the FIFO when it is full. If push is enabled when FIFO is full, old samples are lost. If FIFO\_RO is not set, the new sample is dropped and the FIFO is not updated.

#### A\_FULL\_TYPE (Address 0x0A)

The A\_FULL\_TYPE bit defines the behavior of the A\_FULL interrupt. If the A\_FULL\_TYPE bit is set low, the A\_FULL

interrupt gets asserted when the A\_FULL condition is detected and cleared by status register read, but reasserts for every sample if the A\_FULL condition persists. If A\_FULL\_TYPE bit is set high, the A\_FULL interrupt gets asserted only when a new A\_FULL condition is detected. The interrupt gets cleared on Interrupt Status 1 register read, and does not reassert for every sample until a new A\_FULL condition is detected.

#### FIFO\_STAT\_CLR (Address 0x0A)

The FIFO\_STAT\_CLR bit defines whether the A-FULL interrupt should get cleared by FIFO\_DATA register read. If FIFO\_STAT\_CLR is set low, A\_FULL and DATA\_RDY interrupts do not get cleared by FIFO\_DATA register read but get cleared by status register read. If FIFO\_STAT\_CLR is set high, A\_FULL and DATA\_RDY interrupts get cleared by a FIFO\_DATA register read or a status register read.

#### FLUSH FIFO (Address 0x0A)

The FIFO Flush bit is used for flushing the FIFO. The FIFO becomes empty and the FIFO\_WR\_PTR[6:0], FIFO\_RD\_PTR[6:0], FIFO\_DATA\_COUNT[7:0] and OVF\_COUNTER[6:0] get reset to zero. FLUSH\_FIFO is a self-clearing bit.

#### TIME\_STAMP\_EN (Address 0x0A)

When TIME\_STAMP\_EN bit is set to 1, the 19 bits time stamp gets pushed to the FIFO along with its Tag for every 8 samples. This timestamp is useful for aligning data from two devices after the host reads the FIFOs of those devices. When TIME\_STAMP\_EN bit is set to 0, the sample counter is not pushed to FIFO.

#### Pseudo-Code Example of Initializing the Optical AFE

The following pseudo-code shows an example of configuring MAX86140/MAX86141 for a SpO2 applications, where LED1 and LED2 are IR and red LED, respectively.

```

DEVICE OPEN

START;

// AFE Initialization

WRITE 0x1 to RESET[0];

// Soft Reset (Register 0x0D[0])

DELAY 1ms;

READ Interrupt Status 1;  // Clear Interrupt (Register 0x00)

READ Interrupt Status 2;  // Clear Interrupt (Register 0x01)

WRITE 0x1 to SHDN[0];  // Shutdown (Register 0x0D[1])

WRITE 0x3 to PPG_TINT[1:0];  // Pulse Width = 123.8ms (Register 0x11[1:0])

WRITE 0x2 to PPG1_ADC_RGE1:0];  // ADC Range = 16µA (Register 0x11[3:2])

WRITE 0x2 to PPG2_ADC_RGE1:0];  // ADC Range = 16µA (Register 0x11[3:2])

// For MAX86141 when used in Dual Channel only

// For MAX86141 when used in Dual Channel only

WRITE 0x1 to LP Mode[0];

// Low Power mode enabled

// FIFO Configuration

WRITE 0x0 to LEDC3[3:0];

WRITE 0x0 to LEDC4[3:0];

WRITE 0x0 to LEDC5[3:0];

WRITE 0x0 to LEDC6[3:0];

WRITE 0x0 to SHDN[0];

// Start Sampling STOP;

```

## Pseudo-Code for Interrupt Handling with FIFO\_A\_FULL

The following pseudo-code shows an example on handling the Interrupt when using A\_FULL Interrupt.

int i;

void device data read(void) {

#### Pseudo-Code Example of Reading Data from FIFO

#define FIFO SAMPLES (128-0x10) // FIFO A FULL[6:0] = 0x10

Example pseudo-code for reading data from FIFO when using single photodiode channel and two LED channels.

```

uint8 t sampleCnt;

uint8 t dataBuf[FIFO SAMPLES*3]; //(128 - FIFO A FULL[6:0]) samples, 3 byte/channel

uint8_t tag1[FIFO_SAMPLES/2]; //(128 - FIFO_A_FULL[6:0])/2channels samples

uint8 t tag2[FIFO SAMPLES/2]; //(128 - FIFO A FULL[6:0])/2channels samples

int led1[FIFO SAMPLES/2]; //(128 - FIFO A FULL[6:0])/2channels samples

int led2[FIFO SAMPLES/2]; //(128 - FIFO A FULL[6:0])/2channels samples

ReadReg(0x07, \&sampleCnt); // sampleCnt should be the same value as FIFO SAMPLES

//Read FIFO

ReadFifo(dataBuf, sampleCnt * 3);

for ( i = 0; i < sampleCnt/2/*channels*/; <math>i++ ) {

tag1[i] = (dataBuf[i*6+0] >> 3) & 0x1f;

led1[i] = ((dataBuf[i*6+0] << 16) | (dataBuf[i*6+1] << 8) | (dataBuf[i*6+2]))

& 0x7ffff;

tag2[i] = (dataBuf[i*6+3] >> 3) & 0x1f;

led2[i] = ((dataBuf[i*6+3] << 16) | (dataBuf[i*6+4] << 8) | (dataBuf[i*6+5]))

& 0x7ffff;

}

}

Example pseudo-code for reading data from FIFO when using dual photodiode channels and two LED channels.

#define FIFO SAMPLES (128-0x10) // FIFO A FULL[6:0] = 0x10

void device data read(void) {

int i;

uint8 t sampleCnt;

uint8 t dataBuf[FIFO SAMPLES*3]; //(128 - FIFO A FULL[6:0]) samples, 3 byte/channel

uint8 t tag1A[FIFO SAMPLES/4]; //(128 - FIFO A FULL[6:0])/4channels samples

uint8_t tag1B[FIFO_SAMPLES/4]; //(128 - FIFO_A_FULL[6:0])/4channels samples

uint8_t tag2A [FIFO_SAMPLES/4]; //(128 - FIFO_A_FULL[6:0])/4channels samples

uint8 t tag2B [FIFO SAMPLES/4]; //(128 - FIFO A FULL[6:0])/4channels samples

int led1A[FIFO SAMPLES/4];

int led1B[FIFO SAMPLES/4];

int led2A[FIFO SAMPLES/4];

int led2B[FIFO SAMPLES/4];

ReadReg(0x07, &sampleCnt); // sampleCnt should be the same value as FIFO SAMPLES

//Read FIFO

ReadFifo(dataBuf, sampleCnt * 3);

for ( i = 0; i < sampleCnt/4/*channels*/; <math>i++ ) {

tag1A[i] = (dataBuf[i*12+0] >> 3) & 0x1f;

led1A[i] = ((dataBuf[i*12+0] << 16) | (dataBuf[i*12+1] << 8) |

dataBuf[i*12+2])) & 0x7ffff; // LED1, PD1

tag1B[i] = (dataBuf[i*12+3] >> 3) & 0x1f;

led1B[i] = ((dataBuf[i*12+3] << 16) | (dataBuf[i*12+4] << 8) |

(dataBuf[i*12+5])) & 0x7ffff; // LED1, PD2

tag2A[i] = (dataBuf[i*12+6] >> 3) & 0x1f;

led2A[i] = ((dataBuf[i*12+6] << 16) | (dataBuf[i*12+7] << 8) |

(dataBuf[i*12+8])) & 0x7ffff; // LED2, PD1

tag2B[i] = (dataBuf[i*12+9] >> 3) & 0x1f;

led2B[i] = ((dataBuf[i*12+9] << 16) | (dataBuf[i*12+10] << 8) |

(dataBuf[i*12+11])) & 0x7ffff; // LED2, PD2

```

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

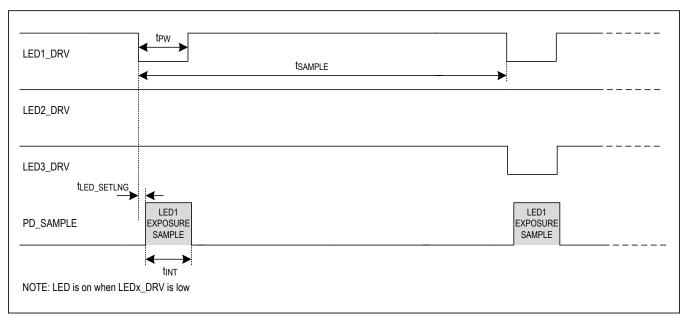

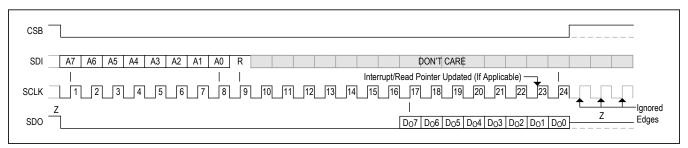

#### **Optical Timing**

The MAX86140/MAX86141 optical controller is capable of being configured to make a variety of measurements. Each LED exposure is ambient light compensated before the ADC conversion.

The controller can be configured to pulse one, two or three LED drivers sequentially so as to make measurements at multiple wavelengths as is done in a pulse oximetry measurements or simultaneously to drive multiple LEDs as is done with heart rate measurements on the wrist.

The controller is also configurable to measure direct ambient level for every exposure sample. The direct ambient measurement can be used to adjust the LED drive level to compensate for increased noise levels when high interfering ambient signals are present.

The following optical timing diagrams illustrate several possible measurement configurations.

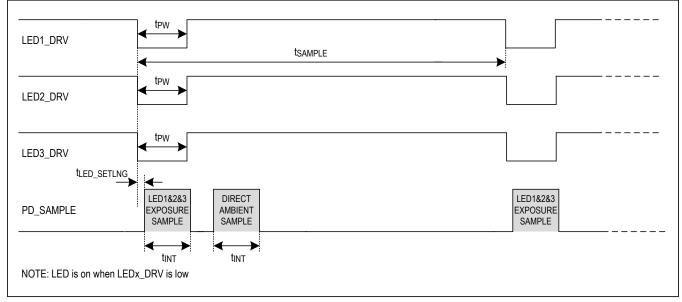

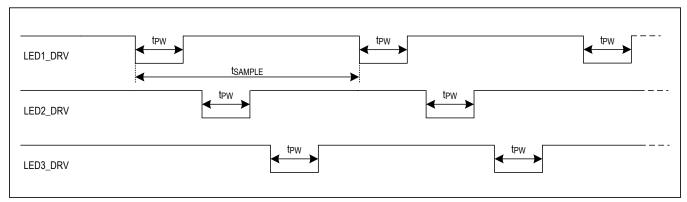

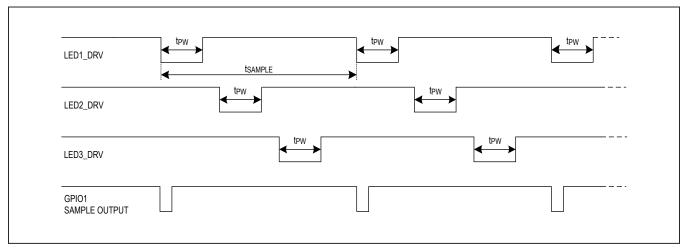

#### One LED Pulsing with No Direct Ambient Sampling

The optical timing diagram below represents just LED1 pulsing during the exposure time with no direct ambient sampling enabled. This timing mode would be used when heart rate is being measured with a single green LED. In this mode a single optical sampled value will appear successively in the FIFO.

Figure 1. Timing for LED1 Pulsing with No Direct Ambient Sampling

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor for Wearable Health

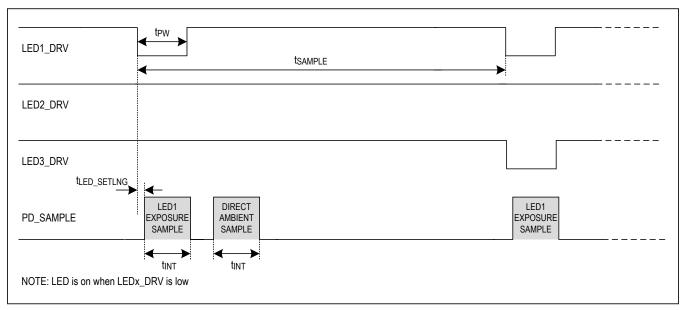

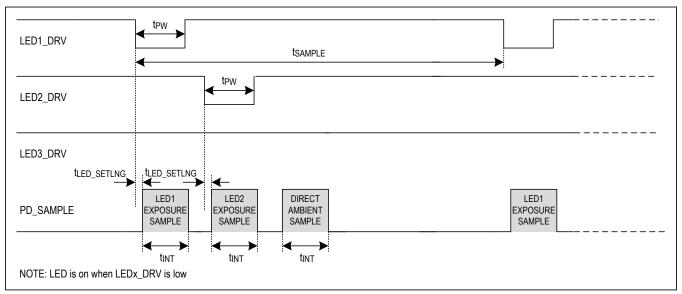

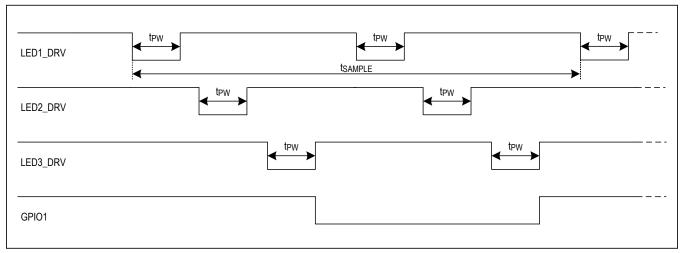

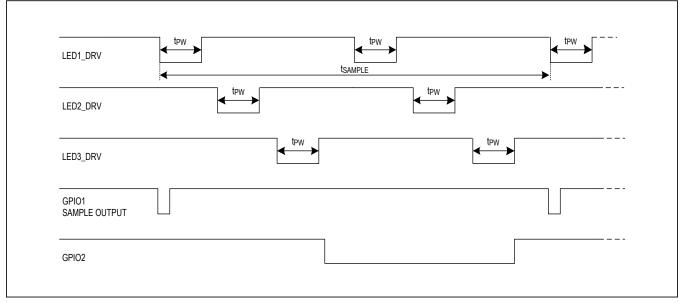

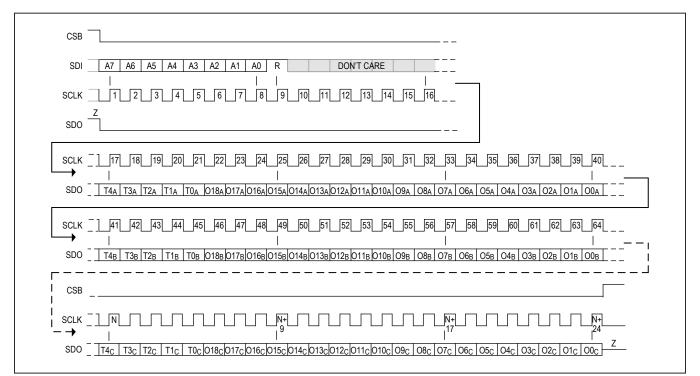

#### One LED Pulsing with Direct Ambient Sampling

The optical timing diagram below represents just LED1 pulsing during the exposure time with direct ambient sampling enabled. This timing mode would be used when heart rate is being measured with a single, green LED. In this mode a single optical sampled value followed by the ambient sampled value will appear successively in the FIFO.

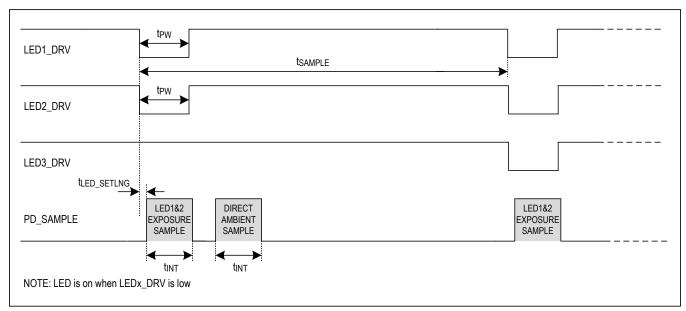

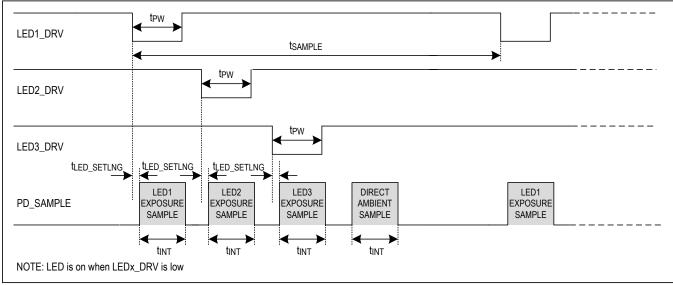

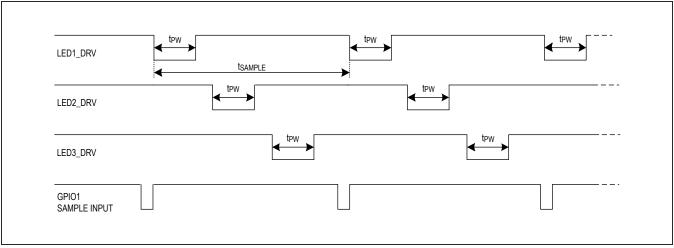

## Two LEDs Pulse Simultaneously with Direct Ambient Sampling

The optical timing diagram below represents both LED1 and LED2 pulsing simultaneously with direct ambient sampling enabled. This timing mode would be used when heart rate is being measured with two green LEDs. In this mode a single optical sampled value followed by the ambient sampled value will appear in successive the FIFO locations. The direct ambient sampling is typically used to compensate the LED drive levels as the optical noise level can be elevated from ambient shot noise.

Figure 2. Timing for LED1 Pulsing with Direct Ambient Sampling

## All LED Pulsing Simultaneously with Direct Ambient Sampling

The optical timing diagram below represents all three LEDs pulsing simultaneously with direct ambient sampling enabled. This timing mode would be used when heart rate is being measured with three green LEDs. In this

mode, a single optical sampled value, followed by the ambient sampled value, will appear in successive the FIFO locations. The direct ambient sampling is typically used to compensate the LED drive levels as the optical noise level can be elevated from ambient shot noise.

Figure 3. Timing for LED1 and LED2 Pulsing Simultaneously with Direct Ambient Sampling

Figure 4. Timing for LED1, LED2, and LED3 Pulsing Simultaneously with Direct Ambient Sampling

## Two LEDs Pulse Sequentially with Direct Ambient Sampling

The timing diagram below illustrates the optical timing when both LED1 and LED2 are enabled to pulse sequentially and direct ambient sampling is also enabled. This timing mode would be used when SpO<sub>2</sub> is being measured with IR and red LEDs. The optical sampled value for each LED will appear successively, followed by the direct ambient sampled value in the FIFO. when SpO<sub>2</sub> is being measured with IR and red LEDs. The optical sampled value

for each LED will appear successively, followed by the direct ambient sampled value in the FIFO.

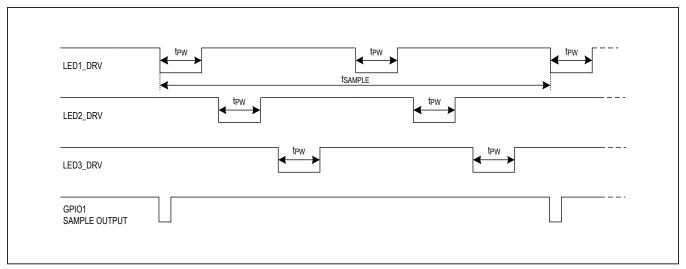

## All LEDs Pulse Sequential with Direct Ambient Sampling

The optical timing diagram below illustrates the three LEDs pulsing sequentially, followed by a direct ambient sample. This timing mode would be used when heart rate on a green LED is combined with and SpO<sub>2</sub> measurement using IR and red LEDs.

Figure 5. Timing for LED1 and LED2 Pulsing Sequentially with Direct Ambient Sampling

Figure 6. Timing for LED1, LED2, and LED3 Pulsing Sequentially with Direct Ambient Sampling

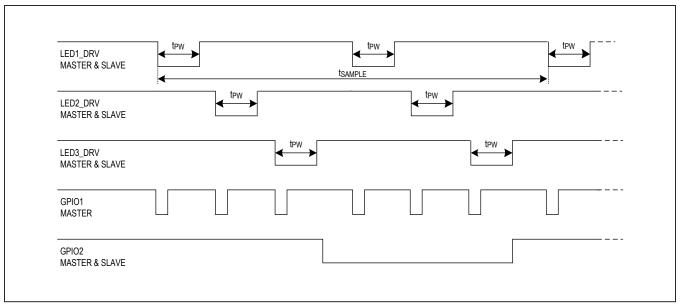

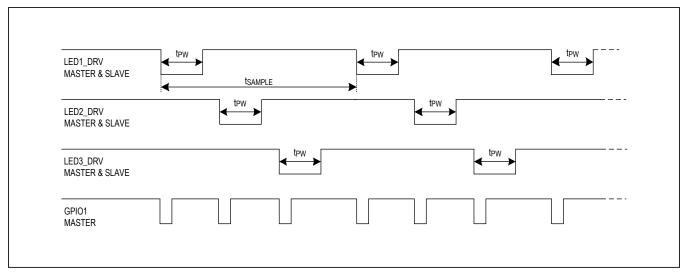

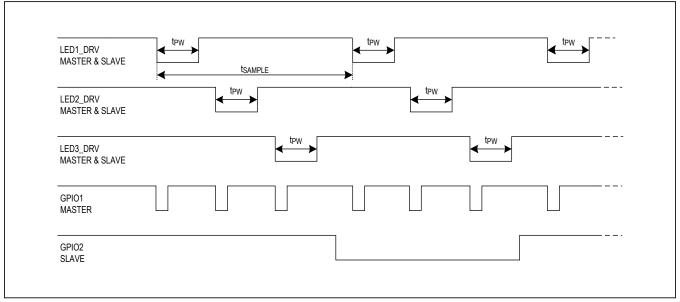

#### **GPIO Configuration**

The MAX86140/MAX86141 support several means by which they can synchronize to external sensors, muxes, and be extended to allow for more flexibility in the measurement configuration. This functionality is extended through the GPIO1 and GPIO2 pins and is selected by the GPIO CTRL bit field in the PPG SYNC Control register (0x10). The following describes option and the functional state of GPIO1 and GPIO2 as well as the part behavior.

#### GPIO CTRL[3:0] 0000 and 0001: Stand Alone With and Without External Mux

Table 7. GPIO Mode 0000 and 0001

| GPIO<br>CTRL | GPIO1<br>FUNCTION          | GPIO2<br>FUNCTION                             | COMMENT                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|----------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000         | Tristate or<br>Mux Control | Disabled                                      | GPIO1 will be active if any of the LEDCn[3:0] states A, B, or C are enabled in the exposure sequence. In this case, GPIO1 will be low during exposures on LED4, LED5 or LED6, otherwise it will be high. If LEDCn[3:0] state A, B, or C is not enabled in the exposure sequence, GPIO1 will be tristate unless externally pulled up. GPIO2 is disabled. Sample and exposure timing is controlled by the internal 32768Hz oscillator.  |

| 0001         | Tristate or<br>Mux Control | Input<br>32768Hz or<br>32000Hz<br>Clock Input | GPIO1 will be active if any of the LEDCn[3:0] states A, B, or C are enabled in the exposure sequence. In this case, GPIO1 will be low during exposures on LED4, LED5 or LED6; otherwise, it will be high. If LEDCn[3:0] state A, B, or C is not enabled in the exposure sequence, GPIO1 will be tristate unless externally pulled up. GPIO2 is an input 32768/32000Hz. Sample and exposure timing is controlled by GPIO2 clock input. |

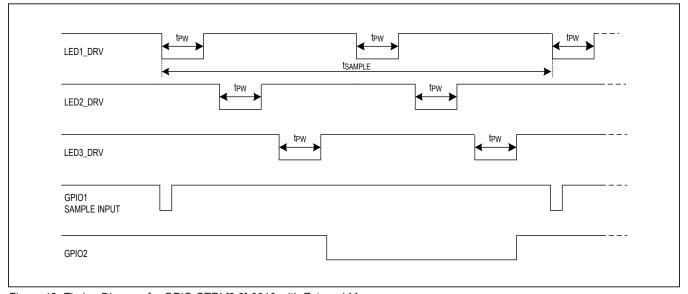

Figure 7. Block Diagram for GPIO CTRL[3:0] 0000 and 0001 Without External Mux

Figure 8. Timing Diagram for GPIO CTRL[3:0] 0000 and 0001 Without External Mux

Figure 9. Timing Diagram for GPIO CTRL[3:0] 0000 and 0001 with External Mux

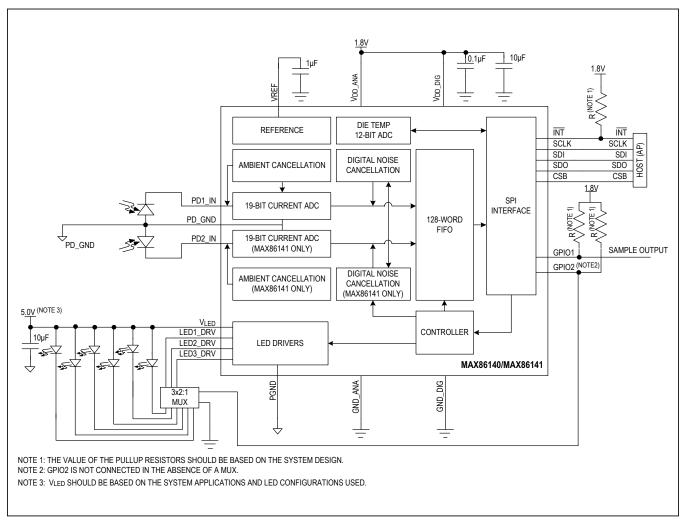

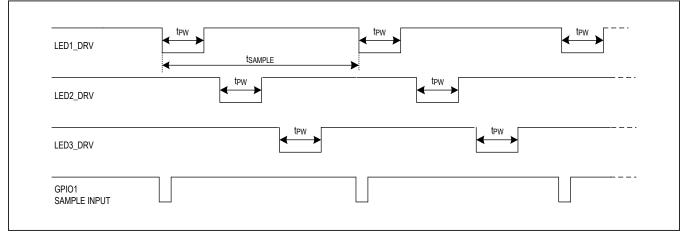

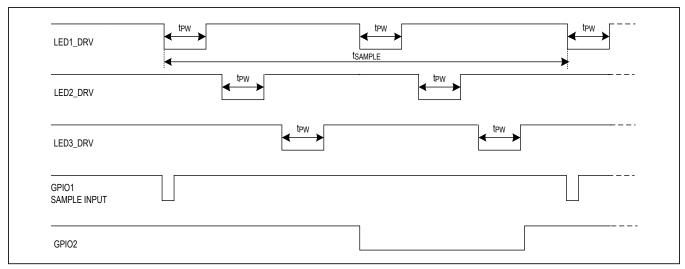

#### GPIO CTRL[3:0] 0010: Start of Sample Input with and without External Mux

Table 8. GPIO Mode 0010

| GPIO CTRL | GPIO1 FUNCTION          | GPIO2 FUNCTION             | COMMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|-------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0010      | Input<br>Sample Trigger | Tristate or<br>Mux Control | GPIO1 is defined as a sample trigger input (Slave). This input can come from an external source or from another MAX86140/ MAX86141 in master sample mode. GPIO2 will be active if any of the LEDCn[3:0] states A, B, or C are enabled in the exposure sequence. In this case, GPIO2 will be low during exposures on LED4, LED5 or LED6, otherwise it will be high. If LEDCn[3:0] state A, B, or C is not enabled in the exposure sequence, GPIO2 will be tristate unless externally pulled up. Exposure timing is controlled by internal oscillator. |

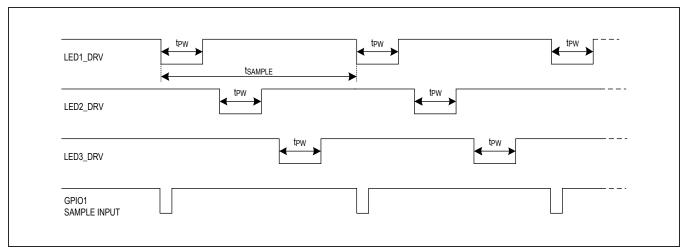

Figure 10. Block Diagram for GPIO CTRL[3:0] 0010 Without External Mux

Figure 11. Timing Diagram for GPIO CTRL[3:0] 0010 Without External Mux

Figure 12. Timing Diagram for GPIO CTRL[3:0] 0010 with External Mux

#### GPIO CTRL[3:0] 0011: Start of Sample Input with External Clock

Table 9. GPIO Mode 0011

| GPIO CTRL | GPIO1<br>FUNCTION       | GPIO2 FUNCTION                             | COMMENT                                                                                                                                                                                                                                                   |

|-----------|-------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0011      | Input<br>Sample Trigger | Input<br>32768Hz<br>or 32000Hz Clock Input | GPIO1 is defined as a sample trigger input (Slave). This input can come from an external source or from another MAX86140/MAX86141 in master sample mode. GPIO2 is an input 32768/32000Hz clock input. Exposure timing is controlled by GPIO2 clock input. |

Figure 13. Block Diagram for GPIO CTRL[3:0] 0011

Figure 14. Timing Diagram for GPIO CTRL[3:0] 0011

## GPIO CTRL[3:0] 0100: Start of Sample Output With and Without External Mux

#### Table 10. GPIO Mode 0100

| GPIO CTRL | GPIO1<br>FUNCTION                     | GPIO2 FUNCTION             | COMMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

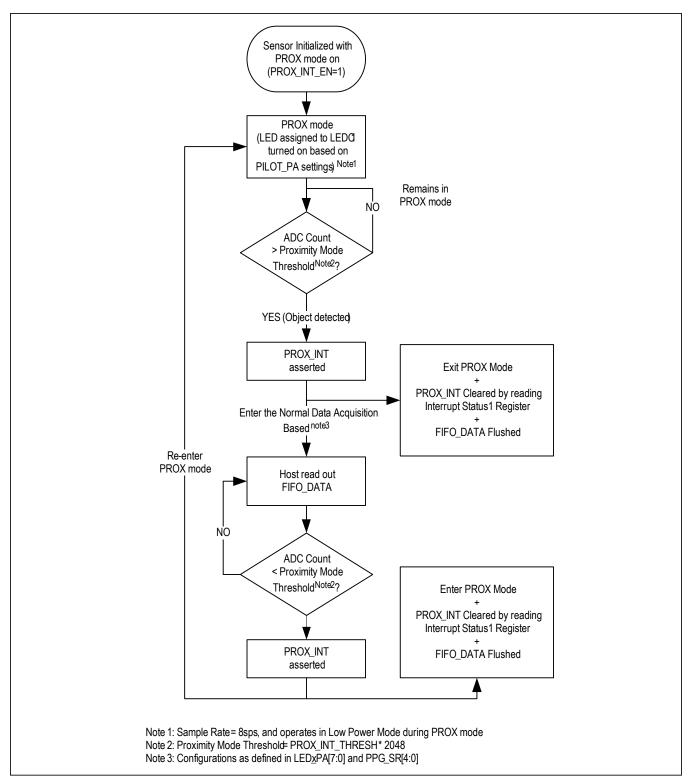

|-----------|---------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|